Maximum quantity allowed is 999

注文本数を選んでください。

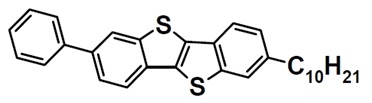

高性能p型半導体材料 “Ph-BTBT-10” の性能評価

Ph-BTBT-10は,近年報告された半導体材料の中でも特に優れた輸送特性を示すp型材料です。半那教授らは,スピンコート法で作製したFET素子においてPh-BTBT-10は酸化物半導体(IGZO)と同等の,極めて高い移動度(μmax = 14.7 cm2/Vs)と大気安定性を併せ持つp型材料であることを報告しています。1)

弊社では,この優れたp型半導体材料であるPh-BTBT-10を製品化しました。社内にて,蒸着法によるOFET素子の作製および評価も行って行っており,最大でホール移動度 μ = 14.0 cm2/Vsが得られています。実験詳細は下記をご参照ください 。

1) H. Iino, T. Usui, J. Hanna, Nat. Commun. 2015, 6, 6828.弊社では,この優れたp型半導体材料であるPh-BTBT-10を製品化しました。社内にて,蒸着法によるOFET素子の作製および評価も行って行っており,最大でホール移動度 μ = 14.0 cm2/Vsが得られています。実験詳細は下記をご参照ください 。

Ph-BTBT-10の性能評価

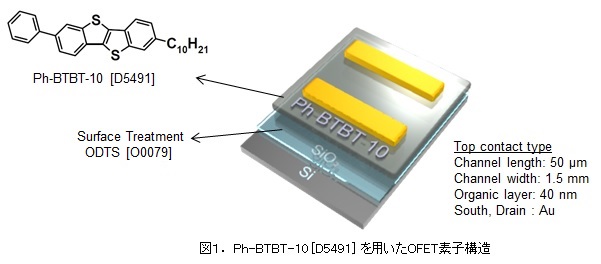

素子作製には,n+-Si/SiO2(SiO2 :200 nm)のbare基板,またはODTS処理基板Trichlorooctadecylsilane (ODTS) [O0079]を用いました。基板を蒸着機にセットし,真空蒸着法により基板加熱下にてPh-BTBT-10 [D5491]の薄膜(40 nm)を形成した後,金(40 nm)を蒸着しソース・ドレイン電極を形成することで,トップコンタクト型OFET素子を作製しました(図1)。その後,大気下にてアニーリング処理(120℃, 5 min)を行い,アニーリング前後のFET特性の比較を行いました。

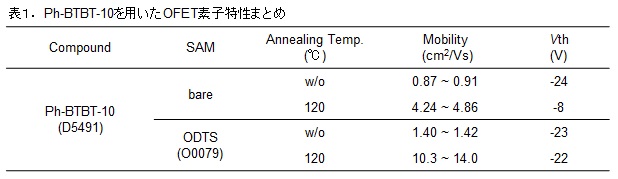

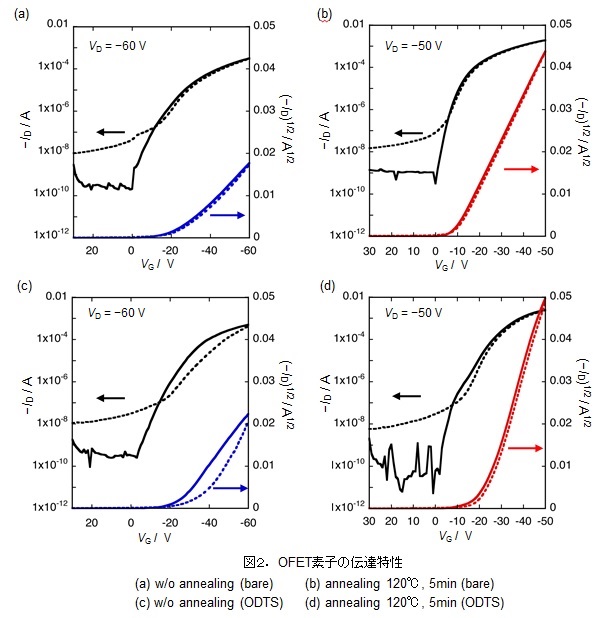

作製した素子の特性を表1および図2に示します。

全ての素子にて,安定したp型半導体特性が観測されました。また,Self-assemble-monolayer (SAM)の有無に関わらず,アニーリング処理(120, 5 min)を行うことでFET性能の大幅な向上が見られました。これは文献と同様に,monolayerからbilayer crystal phase への相転移に起因するものと考えられます1)。bare基板では,ホール移動度μmax = 4.86 cm2/Vs,Vth = -8の良好な値が得られました。ODTS処理基板では,閾値電圧は大きいもののIDSが大幅に増加し,ホール移動度μmax = 14.0 cm2/Vs,Vth = -22 Vの極めて良好な値が得られました。社内装置を用いたFET素子にて,蒸着法で世界トップクラスの半導体特性が観測されています。

今後,アニール処理前後のPh-BTBT-10蒸着膜の膜結晶構造の調査・解析,更なる素子性能の向上・安定化に向けて調査を行います。

「材料の純度」はトランジスタ性能を大きく左右する重要なファクターです。

弊社では,FET素子の作製・解析を行い

実デバイス上で使用できる高品質な材料の安定供給を目指しています。