Maximum quantity allowed is 999

注文本数を選んでください。

有機トランジスタ(OFET)素子作製および評価:anti-DMADT

![anti-DMADT [D4617]](/structure-300/D4617.jpg)

2,8-Dimethylanthra[2,3-b:6,7-b']dithiophene (purified by sublimation)

anti-DMADT

CAS RN: 1019983-99-3

製品コード: D4617

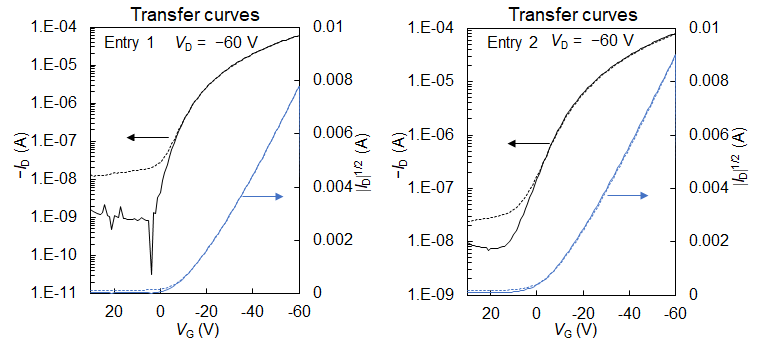

anti-DMADT [D4617]のOFET素子性能評価

![anti-DMADT [D4617] を用いたデバイス作製法・構造](/assets/cms-images/D4617-device-method-structure-en.png)

表. anti-DMADT [D4617]を用いたOFET素子特性

| Entry | Fabrication Method | Device Configuration | SAM Treatment | Tsub (°C) | Annealing Temp.a (°C) | Polarity | μ (cm2 V−1 s−1) | Vth (V) | Ion/Ioff |

|---|---|---|---|---|---|---|---|---|---|

| Entry1 | Fabrication MethodVacuum deposition |

Device ConfigurationTCBG | SAM Treatmentw/o Bare |

Tsub (°C)RT | Annealing Temp.a (°C)w/o | Polarityp | μ (cm2 V−1 s−1)0.11 | Vth (V)‒14 | Ion/Ioff104 |

| Entry2 | Fabrication MethodVacuum deposition |

Device ConfigurationTCBG | SAM Treatmentw/o Bare |

Tsub (°C)RT | Annealing Temp.a (°C)120 | Polarityp | μ (cm2 V−1 s−1)0.11 | Vth (V)‒7.7 | Ion/Ioff104 |

図.伝達特性(飽和領域)

実験詳細

anti-DMADT [D4617]を用いたOFET素子の作製および評価

<基板>

<真空蒸着>

<ポストアニーリング>

<素子構造>

<測定環境>

<基板>

- Bare Si/SiO2 (SiO2膜厚:200 nm)

<真空蒸着>

- anti-DMADT [D4617]の蒸着レート: 0.3 Å/s, (真空度 ∼10−4 Pa)

- 蒸着時の基板温度: RT

- Auの蒸着レート: 1.0 Å/s, (真空度 ∼10−4 Pa)

<ポストアニーリング>

- アニール条件: 120 ºC, 5 min, N2

<素子構造>

- [n+-Si/SiO2 (200 nm) / anti-DMADT [D4617] (60 nm) / Au (40 nm)]

- トップコンタクト・ボトムゲート型 (TCBG)

- チャンネル長: 50 μm

- チャンネル幅: 1.5 mm

<測定環境>

- 窒素雰囲気下

- 電界効果移動度(μ)は伝達特性の飽和領域にて下記式により算出しました

ID = (W/2L) μ Ci (VG − Vth)2